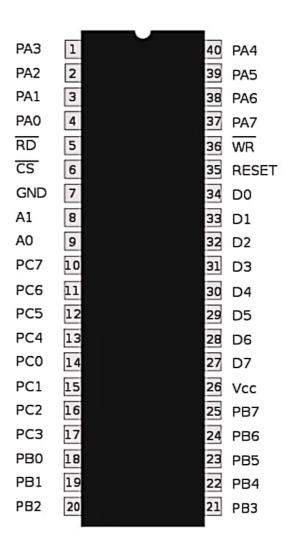

Fig1: Pin diagram of 8255

## I. Functional block of 8255 – Programmable Peripheral Interface (PPI)

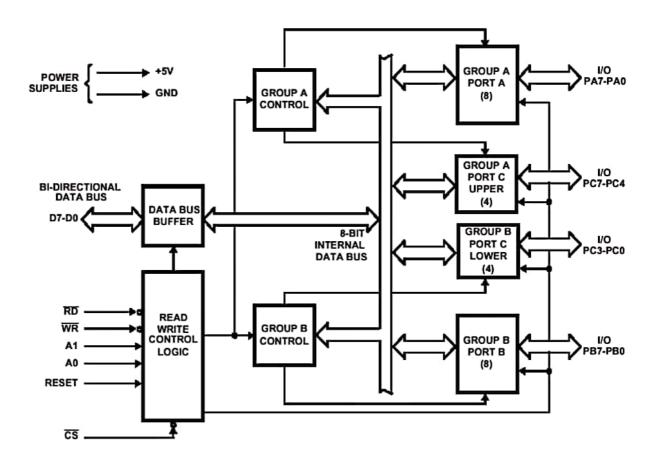

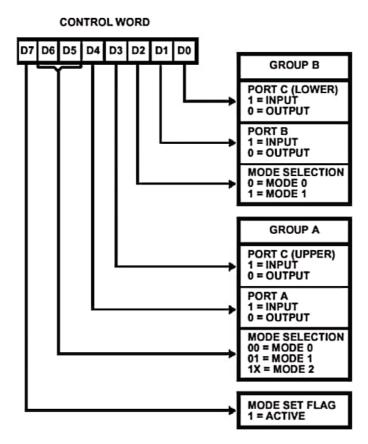

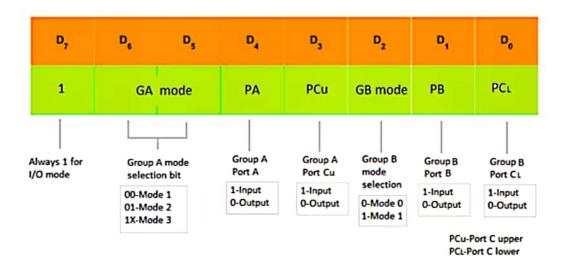

The 8255A has 24 I/O pins that can be grouped primarily in two 8-bit parallel ports: A and B with the remaining eight bits as port C. The eight bits of port C can be used as individual bits or be grouped in to 4-bit ports: CUpper (Cu) and CLower (CL) as in Figure 2. The function of these ports is defined by writing a control word in the control register as shown in Figure 3

Fig 2. Block diagram of 8255

Fig 3. Control word Register format

#### **Data Bus Buffer**

This three-state bi-directional 8-bit buffer is used to interface the 8255 to the system data bus. Data is transmitted or received by the buffer upon execution of input or output instructions by the CPU. Control words and status information are also transferred through the data bus buffer.

### Read/Write and Control Logic

The function of this block is to manage all of the internal and external transfers of both Data and Control or Status words. It accepts inputs from the CPU Address and Control busses and in turn, issues commands to both of the Control Groups.

- (CS) Chip Select. A "low" on this input pin enables the communication between the 8255 and the CPU.

- (RD) Read. A "low" on this input pin enables 8255 to send the data or status information to the CPU on the data bus. In essence, it allows the CPU to "read from" the 8255.

**(WR)** Write. A "low" on this input pin enables the CPU to write data or control words into the 8255.

(A0 and A1) Port Select 0 and Port Select 1. These input signals, in conjunction with the RD and WR inputs, control the selection of one of the three ports or the control word register. They are normally connected to the least significant bits of the address bus (A0 and A1).

(RESET) Reset. A "high" on this input initializes the control register to 9Bh and all ports (A, B, C) are set to the input mode.

| <b>A</b> 1 | Α0 | SELECTION |  |  |

|------------|----|-----------|--|--|

| 0          | 0  | PORT A    |  |  |

| 0          | 1  | PORT B    |  |  |

| 1          | 0  | PORT C    |  |  |

| 1          | 1  | CONTROL   |  |  |

### **Group A and Group B Controls**

The functional configuration of each port is programmed by the systems software. In essence, the CPU "outputs" a control word to the 8255. The control word contains information such as "mode", "bit set", "bit reset", etc., that initializes the functional configuration of the 8255. Each of the Control blocks (Group A and Group B) accepts "commands" from the Read/Write Control logic, receives "control words" from the internal data bus and issues the proper commands to its associated ports.

# Ports A, B, and C

The 8255 contains three 8-bit ports (A, B, and C). All can be configured to a wide variety of functional characteristics by the system software but each has its own special features or "personality" to further enhance the power and flexibility of the 8255.

**Port A** One 8-bit data output latch/buffer and one 8-bit data input latch. Both "pull-up" and "pull-down" bus-hold devices are present on Port A.

Port B One 8-bit data input/output latch/buffer and one 8-bit data input buffer.

**Port C** One 8-bit data output latch/buffer and one 8-bit data input buffer (no latch for input). This port can be divided into two 4-bit ports under the mode control. Each 4-bit port contains a 4-bit latch and it can be used for the control signal output and status signal inputs in conjunction with ports A and B.

### II. Operational modes of 8255

There are two basic operational modes of 8255:

- Bit set/reset Mode (BSR Mode).

- 2. Input/Output Mode (I/O Mode).

The two modes are selected on the basis of the value present at the  $D_7$  bit of the Control Word Register. When  $D_7 = 1$ , 8255 operates in I/O mode and when  $D_7 = 0$ , it operates in the BSR mode.

### 1. Bit set/reset (BSR) mode

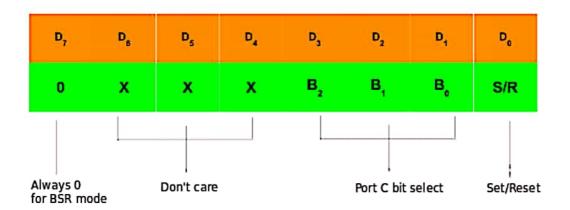

The Bit Set/Reset (BSR) mode is applicable to port C only. Each line of port C ( $PC_0$  -  $PC_7$ ) can be set/reset by suitably loading the control word register as shown in Figure 4. BSR mode and I/O mode are independent and selection of BSR mode does not affect the operation of other ports in I/O mode.

Fig 4: 8255 Control register format for BSR mode

- D<sub>7</sub> bit is always 0 for BSR mode.

- Bits D<sub>6</sub>, D<sub>5</sub> and D<sub>4</sub> are don't care bits.

- Bits D<sub>3</sub>, D<sub>2</sub> and D<sub>1</sub> are used to select the pin of Port C.

- Bit D<sub>0</sub> is used to set/reset the selected pin of Port C.

Selection of port C pin is determined as follows:

| В3 | B2 | B1 | Bit/pin of port C selected |

|----|----|----|----------------------------|

| 0  | 0  | 0  | PC <sub>0</sub>            |

| 0  | 0  | 1  | PC <sub>1</sub>            |

| 0  | 1  | 0  | PC <sub>2</sub>            |

| 0  | 1  | 1  | PC <sub>3</sub>            |

| 1  | 0  | 0  | PC <sub>4</sub>            |

| 1  | 0  | 1  | PC <sub>5</sub>            |

| 1  | 1  | 0  | PC <sub>6</sub>            |

| 1  | 1  | 1  | PC <sub>7</sub>            |

As an example, if it is needed that PC<sub>5</sub> be set, then in the control word,

- 1. Since it is BSR mode, D<sub>7</sub> = '0'.

- 2. Since D<sub>4</sub>, D<sub>5</sub>, D<sub>6</sub> are not used, assume them to be '0'.

- 3.  $PC_5$  has to be selected, hence,  $D_3 = '1'$ ,  $D_2 = '0'$ ,  $D_1 = '1'$ .

- 4.  $PC_5$  has to be set, hence, D0 = '1'.

Thus, as per the above values, 0B (Hex) will be loaded into the Control Word Register (CWR).

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  |

## 2. Input/Output mode

This mode is selected when D<sub>7</sub> bit of the Control Word Register is 1. There are three I/O modes:

- 1. Mode 0 Simple I/O

- 2. Mode 1 Strobed I/O

- 3. Mode 2 Strobed Bi-directional I/O

Figure 5: 8255 Control word for I/O mode

- D<sub>0</sub>, D<sub>1</sub>, D<sub>3</sub>, D<sub>4</sub> are assigned for lower port C, port B, upper port C and port A respectively. When these bits are 1, the corresponding port acts as an input port. For e.g., if D<sub>0</sub> = D<sub>4</sub> = 1, then lower port C and port A act as input ports. If these bits are 0, then the corresponding port acts as an output port. For e.g., if D<sub>1</sub> = D<sub>3</sub> = 0, then port B and upper port C act as output ports as shown in Figure 5.

- D<sub>2</sub> is used for mode selection of Group B (port B and lower port C). When D<sub>2</sub> = 0, mode 0 is selected and when D<sub>2</sub> = 1, mode 1 is selected.

- D<sub>5</sub>& D<sub>6</sub> are used for mode selection of Group A (port A and upper port C). The selection is done as follows:

| D <sub>6</sub> | D <sub>5</sub> | Mode |

|----------------|----------------|------|

| 0              | 0              | 0    |

| 0              | 1              | 1    |

| 1              | X              | 2    |

As it is I/O mode, D<sub>7</sub> = 1.

For example, if port B and upper port C have to be initialized as input ports and lower port C and port A as output ports (all in mode 0):

- 1. Since it is an I/O mode,  $D_7 = 1$ .

- 2. Mode selection bits, D2, D5, D6 are all 0 for mode 0 operation.

- 3. Port B and upper port C should operate as Input ports, hence,  $D_1 = D_3 = 1$ .

- 4. Port A and lower port C should operate as Output ports, hence,  $D_4 = D_0 = 0$ .

Hence, for the desired operation, the control word register will have to be loaded with "10001010" = 8A (hex).

### Mode 0 - simple I/O

In this mode, the ports can be used for simple I/O operations without handshaking signals. Port A, port B provide simple I/O operation. The two halves of port C can be either used together as an additional 8-bit port, or they can be used as individual 4-bit ports. Since the two halves of port C are independent, they may be used such that one-half is initialized as an input port while the other half is initialized as an output port.

The input/output features in mode 0 are as follows:

- Output ports are latched.

- 2. Input ports are buffered, not latched.

- 3. Ports do not have handshake or interrupt capability.

- 4. With 4 ports, 16 different combinations of I/O are possible.

### ➤ Mode 0 – input mode

- In the input mode, the 8255 gets data from the external peripheral ports and the CPU reads the received data via its data bus.

- The CPU first selects the 8255 chip by making ¬CS low. Then it selects the desired port using A₀ and A₁ lines.

- The CPU then issues an ¬RD signal to read the data from the external peripheral device via the system data bus.

### Mode 0 - output mode

- In the output mode, the CPU sends data to 8255 via system data bus and then the external peripheral ports receive this data via 8255 port.

- CPU first selects the 8255 chip by making ¬CS low. It then selects the desired port using A₀ and A₁ lines.

- CPU then issues a ¬WR signal to write data to the selected port via the system data bus. This data is then received by the external peripheral device connected to the selected port.

## > Mode 1

When we wish to use port A or port B for handshake (strobed) input or output operation, we initialise that port in mode 1 (port A and port B can be initialised to operate in different modes, i.e., for e.g., port A can operate in mode 0 and port B in mode 1). Some of the pins of port C function as handshake lines.

For port B in this mode (irrespective of whether is acting as an input port or output port), PC0, PC1 and PC2 pins function as handshake lines.

If port A is initialised as mode 1 input port, then, PC3, PC4 and PC5 function as handshake signals. Pins PC6 and PC7 are available for use as input/output lines.

The mode 1 which supports handshaking has following features:

- 1. Two ports i.e. port A and B can be used as 8-bit i/o ports.

- 2. Each port uses three lines of port c as handshake signal and remaining two signals can be used as i/o ports.

- 3. Interrupt logic is supported.

- 4. Input and Output data are latched.

# Input Handshaking signals

- 1. IBF (Input Buffer Full) It is an output indicating that the input latch contains information.

- 2. STB (Strobed Input) The strobe input loads data into the port latch, which holds the information until it is input to the microprocessor via the IN instruction.

- 3. INTR (Interrupt request) It is an output that requests an interrupt. The INTR pin becomes a logic 1 when the STB input returns to a logic 1, and is cleared when the data are input from the port by the microprocessor.

- 4. INTE (Interrupt enable) It is neither an input nor an output; it is an internal bit programmed via the port PC4(port A) or PC2(port B) bit position.

### **Output Handshaking signals**

1. OBF (Output Buffer Full) - It is an output that goes low whenever data are output(OUT) to the port A or port B latch. This signal is set to a logic 1 whenever the ACK pulse returns from the external device.

- 2. ACK (Acknowledge)-In causes the OBF pin to return to a logic 1 level. The ACK signal is a response from an external device, indicating that it has received the data from the 82C55 port.

- 3. INTR (Interrupt request) It is a signal that often interrupts the microprocessor when the external device receives the data via the signal, this pin is qualified by the internal INTE(interrupt enable) bit.

- 4. INTE (Interrupt enable) It is neither an input nor an output; it is an internal bit programmed to enable or disable the INTR pin. The INTE A bit is programmed using the PC6 bit and INTE B is programmed using the PC2 bit.

### ➤ Mode 2

Only group A can be initialized in this mode. Port A can be used for bidirectional handshake data transfer. This means that data can be input or output on the same eight lines (PA0 - PA7). Pins PC3 - PC7 are used as handshake lines for port A. The remaining pins of port C (PC0 - PC2) can be used as input/output lines if group B is initialized in mode 0 or as handshaking for port B if group B is initialized in mode 1. In this mode, the 8255 may be used to extend the system bus to a slave microprocessor or to transfer data bytes to and from a floppy disk controller. Acknowledgement and handshaking signals are provided to maintain proper data flow and synchronisation between the data transmitter and receiver.